## LOGIC GATES AND ARITHMETIC

Although most home computers can perform the complete range of arithmetic functions, only addition is directly carried out by logic circuits. All other functions, such as subtraction, multiplication and division, are carried out using a combination of hardware 'adder' circuits and software to control the movement of bit patterns. Before we can look at the circuits required to perform binary addition we must look at the process itself. Let us consider the following binary addition:

|         | 85 | 45 | 25 | 15 |

|---------|----|----|----|----|

|         | 0  | 1  | 0  | 1  |

|         | 0  | 1  | 1  | 1  |

|         | 1  | 1  | 0  | 0  |

| CARRIES | 1  | 1  | 1  |    |

If we take one column of the sum in isolation say the twos column — we can list the various inputs and outputs to and from that column. The inputs are: the two bits to be added, and the carry bit from the previous column. The outputs are: the bit put into the twos column in the answer, and the bit to be carried into the next column. A device that would accept these inputs and produce the correct outputs is known as an *adder*: This device is rather complex so let us start with a slightly simplified version, known as a half adder. A half adder circuit ignores the fact that there may be a carry from a previous column. This reduces the problem to a circuit with two inputs and two outputs. We can now devise a truth table for a half adder circuit, which looks like this:

| IMPUTE | OUTDUTE |  |  |

|--------|---------|--|--|

| INPUTS | OUTPUTS |  |  |

| 1st BIT | 2nd BIT | CARRY BIT | ANSWER BIT |

|---------|---------|-----------|------------|

| 0       | 0       | 0         | 0          |

| 0       | 1       | 0         | 1          |

| 1       | 0       | 0         | 1          |

| 1       | 1       | 1         | 0          |

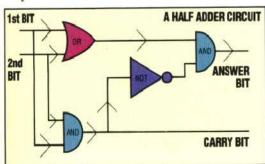

It is easy to see that the carry bit will be one if the first bit AND the second bit are both one. The answer bit is formed by ORing the inputs together, except in the case when the carry bit is one. We may describe the answer bit output as being one if: 'the first bit is one OR the second bit is one, and NOT if the carry bit is one'. The following circuit will produce the required outputs:

## **EXERCISE 2**

- 1) Draw logic circuits for the following Boolean expressions:

- a) X = (A + B).C

- b) X = A.B + (A + C)

- c)  $X = \overline{A}.B + (A + B)$

- d)  $X = \overline{A.B.}(A + B)$

- 2) Write down the Boolean expression using A and B as inputs for the carry bit and the answer bit of a half adder circuit.

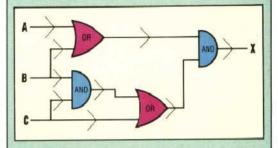

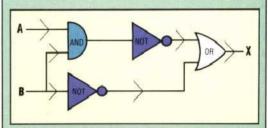

- 3) Write down the Boolean expressions for these circuits:

## Answers to Exercise 1 On Page 9

11

| PASSED DRIVING<br>TEST | ACCOMPANIED BY QUALIFIED DRIVER | ALLOWED TO<br>DRIVE |

|------------------------|---------------------------------|---------------------|

| FALSE                  | FALSE                           | FALSE               |

| FALSE                  | TRUE                            | TRUE                |

| TRUE                   | FALSE                           | TRUE                |

| TRUE                   | TRUE                            | TRUE                |

2)

| CASSETTE<br>PLAYER<br>AVAILABLE | DISK DRIVE<br>AVAILABLE | WRITTEN FOR<br>DIFFERENT<br>COMPUTER | PROGRAM<br>WILL<br>LOAD |

|---------------------------------|-------------------------|--------------------------------------|-------------------------|

| FALSE                           | FALSE                   | FALSE                                | FALSE                   |

| FALSE                           | FALSE                   | TRUE                                 | FALSE                   |

| FALSE                           | TRUE                    | FALSE                                | TRUE                    |

| FALSE                           | TRUE                    | TRUE                                 | FALSE                   |

| TRUE                            | FALSE                   | FALSE                                | TRUE                    |

| TRUE                            | FALSE                   | TRUE                                 | FALSE                   |

| TRUE                            | TRUE                    | FALSE                                | TRUE                    |

| TRUE                            | TRUE                    | TRUE                                 | FALSE                   |

3)

| A | В | P | Q | C |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |